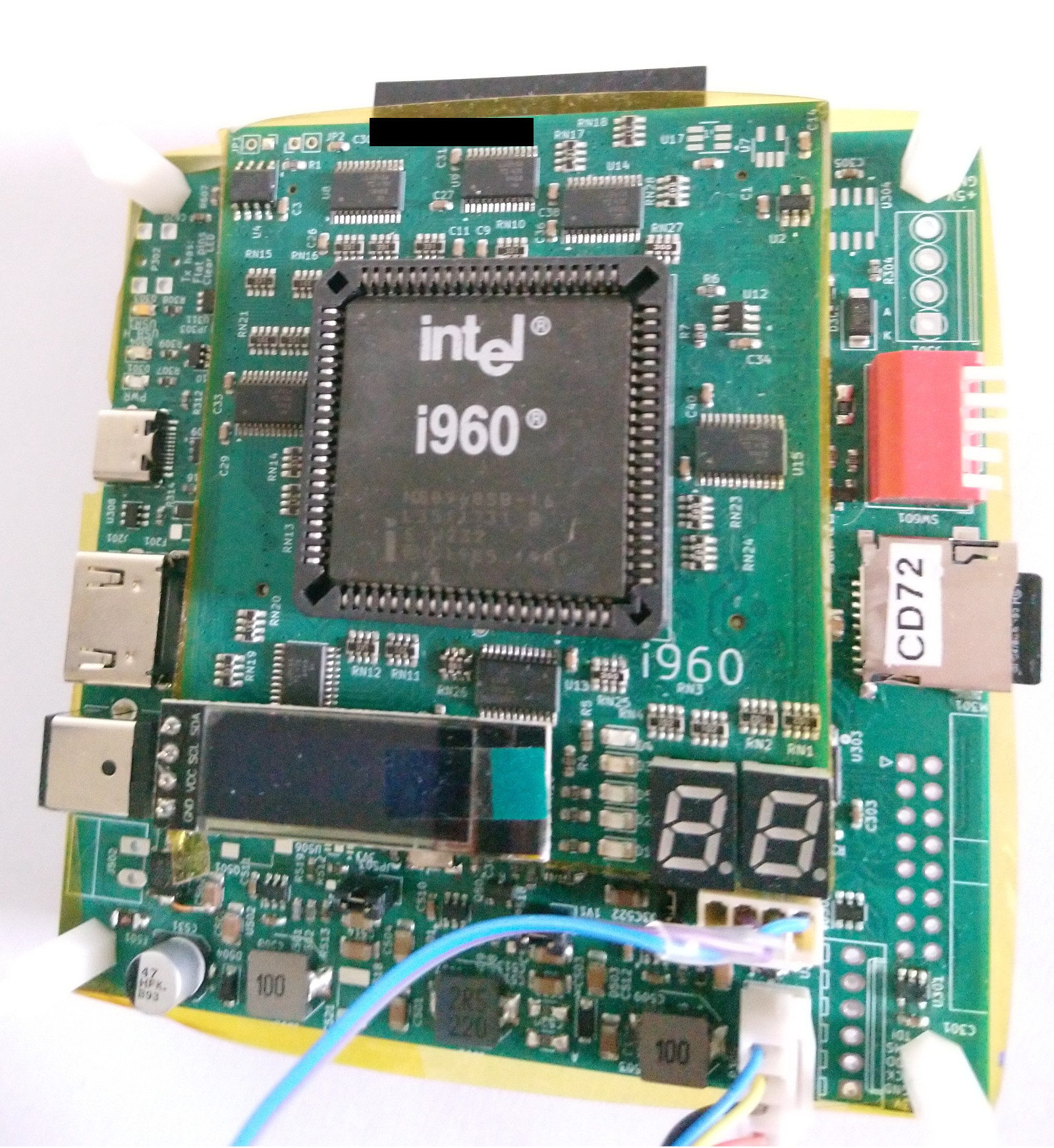

Another processor module, but this time a less successful one - a board based around the Intel i960 (specifically the 80960SA / 80960SB). The i960 is one of the more challenging processors I've worked with, for a few reasons:

- The compiler situation is pretty bad - GCC removed i960 support a very long time ago (some time in approx. 2006)

- The i960 requires some complex data structures in memory to boot, one of which needs a checksum

- The processor bus requires the ability to handle read/write bursts, rather than being an optional performance improvement.

- Documentation for the i960SA/SB is quite sparse (although the wayback machine has archived the Refererence Manual

The status of the project is:

- There's a small error in the schematic.the direction of the level shifters on bits A31..A16 should always be from processor to FPGA, rather than switched with the data bus.

- This isn't a major issue, as in FPGA, prior to turning the bus around, the levels of A31..A16 can be captured so that when the bus is turned around, there's no contention

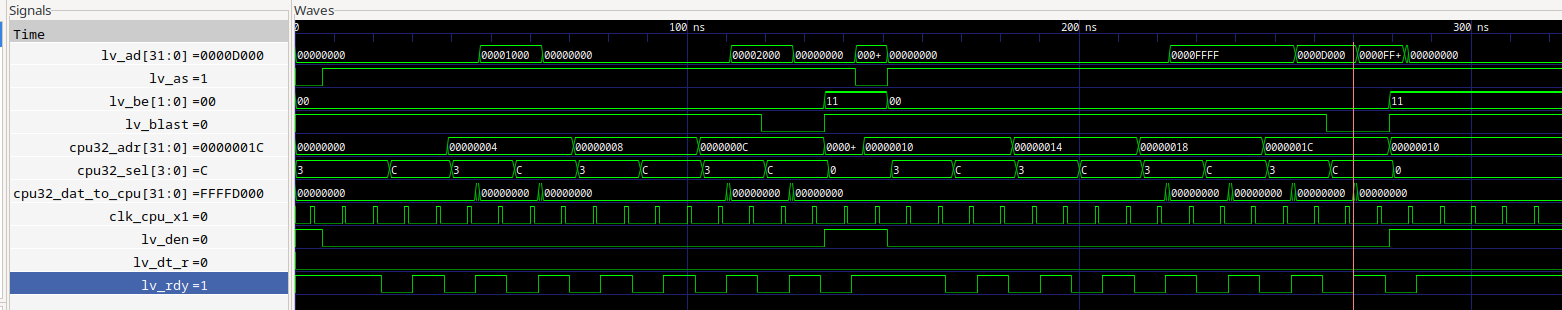

- The i960 is able to validate the initial checksum, and jumps to the location of the Instruction Pointer specified in the System Address Table (SAT)

- I see a number of instruction are fetched, but the instructions don't seem to be running, and after a while the instruction fetches stop.

- Swapping around the words of the instruction (in case it was an endinanness issue) results in the fault handler running.

In case it's useful for anyone else trying to get the checksum correct, here's an example of a working SAT (I've included a Python script used to calculate it at the end of this page):

| Address | Value | Comment |

|---|---|---|

| 0x00 | 0x00000000 | SAT pointer |

| 0x04 | 0x00001000 | PRCB pointer |

| 0x08 | 0x00000000 | |

| 0x0C | 0x00002000 | Instruction Pointer |

| 0x10 | 0x00000000 | |

| 0x14 | 0x00000000 | |

| 0x18 | 0xFFFFFFFF | |

| 0x1C | 0xFFFFD000 | Checksum |

Note that the Processor Control Block (PRCB) also needs to contain specific values at certain locations (it's used to configure the i960).

Here's a view of the waveforms on startup:

At some point, I'll return to this project after a bit of a break, and see if I can make any more progress - but for the moment, I've parked it.

Some design resources are here, but should be viewed with caution - as the project isn't working!

- modular_cpu_80960sb.pdf

- i960_checksum.py Script to calculate the checksum of the SAT

- modular_cpu_i960_boot_fail.zip Waveforms from a failing startup (where the processor fault handler is being called)

- wb_cpu_bus_i960sb.sv i960 bus to Wishbone bridge